Difference between revisions of "Intel 8086"

(→Pipeline Design) |

(→Memory Segmentation) |

||

| Line 65: | Line 65: | ||

To overcome the 16‑bit limitation of its registers while still addressing 1 MB of memory, the 8086 employs a segmented memory model. | To overcome the 16‑bit limitation of its registers while still addressing 1 MB of memory, the 8086 employs a segmented memory model. | ||

| − | In this scheme, memory addresses | + | In this scheme, the BIU forms memory addresses by shifting a 16‑bit segment register four bits to the left and then adding a 16‑bit offset. This results in a 20‑bit physical address. |

Although this model can be seen as complex, it allowed small programs (fitting within a 64‑KB segment) to be loaded at a fixed offset, simplifying relocation in many cases. | Although this model can be seen as complex, it allowed small programs (fitting within a 64‑KB segment) to be loaded at a fixed offset, simplifying relocation in many cases. | ||

Revision as of 18:02, 7 February 2025

The Intel 8086 is a landmark 16‑bit microprocessor introduced by Intel in 1978. It was the first in the x86 family and established many architectural conventions that continue to influence modern personal computing.

With a hybrid internal design—featuring 16‑bit registers and a 16‑bit arithmetic logic unit (ALU) paired with a 20‑bit external address bus—the 8086 could directly address 1 megabyte of memory, a significant leap over its 8‑bit predecessors.

Although there were definitely other CPUs in use in the 1980s, the vast majority of microcomputers people had at home or at the office used either a MOS 6502 (or one of its variants), a Zilog Z80, an early member of the Intel 8086 family, or a Motorola 68000.

Contents

History

After the release of the 8080 CPU, Intel began working on the iAPX 432 project. It was an ambitious 32‑bit design—aimed at supporting advanced, high‑level programming features in hardware—which took several years and a large team to develop, partly because it awaited further improvements in chip density per Moore’s Law.

Meanwhile, to quickly counter the competition, Intel rushed a simpler, lower‑risk design: the 8086. This chip, developed as an incremental evolution of the 8080 and managed by a separate team, was ready for mass market in 1978.

The chip’s design was partly influenced by the need to maintain some backward compatibility with 8‑bit software while also providing a richer instruction set for high‑level languages such as Pascal and PL/M.

Although the IBM PC later used the nearly identical 8088 (which featured an 8‑bit external data bus for cost savings), the 8086 itself became the architectural blueprint for the x86 family, directly influencing later processors.

As for the iAPX 432, it turned out to be a commercial failure, and was discontinued in 1986. Intel then tried to venture into RISC CPUs in the late 1980s with the i860 and i960. But it was ultimately unsuccessful.

Architecture

Most sources claim that the 8086 has about 29,000 transistors. But actually, it has only 19,618 transistors. Source

To put it into perspective, 64KB of DRAM contains 524,288 transistors, as 1 bit of DRAM needs 1 transistor.

Fun fact: The original IBM PC came with 16KB of memory. Source

Microcode

Whereas the Z80 and the 6502 CPUs use a Decode ROM (PLA), the 8086 uses microcode instead.

To execute a machine instruction, the computer internally executes several simpler micro-instructions, specified by the microcode. In other words, microcode forms another layer between the machine instructions and the hardware.

The 8086's microcode ROM holds 512 micro-instructions, each 21 bits wide. The microcode engine is assisted by two smaller ROMs: the "Group Decode ROM" to categorize machine instructions, and the "Translation ROM" to branch to microcode subroutines for address calculation and other roles.

See: Group Decode ROM viewer How the 8086 processor's microcode engine works Undocumented 8086 instructions, explained by the microcode 8086 microcode disassembled

Reverse-engineering the: multiplication algorithm division microcode string operations conditional jumps register codes ModR/M addressing microcode instructions length flags circuitry interrupt circuitry HALT circuitry ALU circuitry in the Intel 8086 processor

Pipeline Design

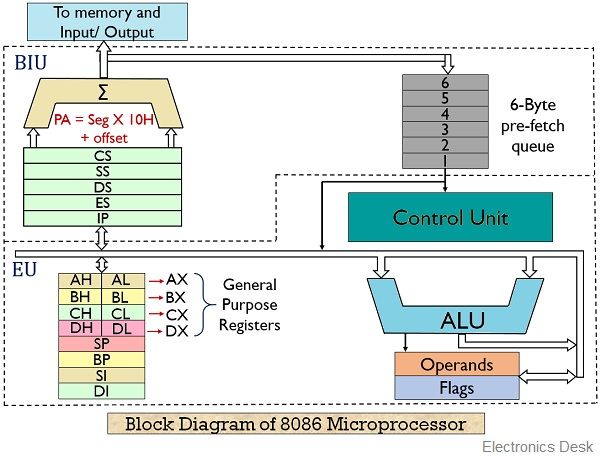

Internally, the 8086 features a 16‑bit execution unit (EU) that performs arithmetic, logic, and control functions, while simultaneously a separate bus interface unit (BIU) handles all data transfers and external communications.

The BIU includes a 6‑byte prefetch queue (4-byte for 8088). The EU fetches instructions from the prefetch queue (not directly from memory). It has no direct connection to the external system bus, relying entirely on the BIU for data and instruction access.

Since EU and BIU are independent, whenever the EU starts decoding and executing fetched instructions, the BIU actively fetches additional instruction bytes to keep the queue filled.

Only the BIU differs between the 8088 and 8086. As the EU is the same for both, the programming instructions are exactly the same for each. Programs written for the 8086 can be run on the 8088 without any changes.

See: The 8086 processor's microcode pipeline from die analysis Intel 8088 processor's instruction prefetch circuitry Inside the Intel 8088 processor's bus interface state machine

Block Diagrams

Memory Segmentation

To overcome the 16‑bit limitation of its registers while still addressing 1 MB of memory, the 8086 employs a segmented memory model.

In this scheme, the BIU forms memory addresses by shifting a 16‑bit segment register four bits to the left and then adding a 16‑bit offset. This results in a 20‑bit physical address.

Although this model can be seen as complex, it allowed small programs (fitting within a 64‑KB segment) to be loaded at a fixed offset, simplifying relocation in many cases.

See: Reverse-engineering the 8086 processor's address and data pin circuits

Register Structure

The 8086 provides fourteen 16‑bit registers. Its register file includes:

- Data Registers: AX (accumulator), BX (base), CX (counter), and DX (data). Each accessible as high (AH, BH, CH, DH) and low (AL, BL, CL, DL) 8‑bit registers.

- Pointer and Index Registers: SP (stack pointer), BP (base pointer), SI (source index), and DI (destination index) used for addressing and data manipulation.

- Segment Registers: CS (code), DS (data), SS (stack), and ES (extra) which define the memory segments for program code, data, and the stack.

- Instruction Pointer and Flags: A 16‑bit instruction pointer (IP) and a 16‑bit status register (Flags). This register includes six status flags (zero, carry, sign, overflow, parity, and auxiliary carry) to indicate the outcomes of operations. It also contains three control flags: the Direction Flag controls the direction in which string instructions act, the Interrupt Flag to enable/disable interrupts and the Trap Flag for single-step debugging.

Instruction Set

As a complex instruction set computer (CISC), the 8086 supports a rich array of operations, including multiple addressing modes such as register, immediate, and memory addressing.

The 8086's instruction set was designed with a new concept, the "ModR/M" byte, which usually follows the opcode byte. The ModR/M byte specifies the memory addressing mode and the register (or registers) to use, allowing that information to be moved out of the opcode.

Although most operations execute on 16‑bit operands, the chip allows manipulation of 8‑bit data as well—an important feature for compatibility with legacy 8‑bit software.

See: Tracing the roots of the 8086 instruction set to the Datapoint 2200 minicomputer

Links

- Intel 8086 at the English-language Wikipedia

- Pin diagram of 8086

- Intel Microprocessors Practical Reference

- 8086 Programmer's Pocket Reference Guide

- Micro Chart 8086 CPU reference card

- Tom Harte's SingleStepTests