Motorola 68000

The Motorola 68000 (commonly abbreviated as 68k) is a landmark microprocessor introduced in 1979 by Motorola Semiconductor.

It is frequently characterized as a “16/32‑bit” processor as its design exhibits a unique hybrid architecture: the programming model is 32‑bit (with 32‑bit registers and a 32‑bit instruction set), yet its data arithmetic is carried out by a 16‑bit arithmetic logic unit (ALU) and it utilizes a 16‑bit external data bus. Its 24‑bit address bus enables direct access to 16 megabytes of memory, a very large space for the era.

This compromise made it possible to fit the CPU within a 64-pin package while not resorting to multiplexing pins.

Although there were definitely other CPUs in use in the 1980s, the vast majority of microcomputers people had at home or at the office used either a MOS 6502 (or one of its variants), a Zilog Z80, an early member of the Intel 8086 family, or a Motorola 68000.

Contents

History

Motorola developed the 68000 in the late 1970s to compete with emerging 16‑bit designs and to counter the limitations of 8‑bit microprocessors like the Motorola 6800. In late 1976, Motorola was aware that Intel was working on a 16-bit extension of their 8080 series, which would emerge as the Intel 8086. They knew that if they launched a product similar to the 8086, within 10% of its capabilities, Intel would outperform them in the market. Another 16-bit would not do, their design would have to be bigger, and that meant having some 32-bit features.

The Motorola Advanced Computer System on Silicon (MACSS) project was created to build the design, with Tom Gunter to be its principal architect. The performance goal was set at 1 million instructions per second (MIPS). The external interface was reduced to 16 data pins and 24 for addresses, allowing it all to fit in a 64-pin package.

The success of the 68000 spurred a family of processors (68010, 68020, 68030, 68040, 68060) that gradually incorporated full 32‑bit ALUs, on‑chip caches, and integrated MMUs and FPUs. Despite these advances, the original 68000 remained widely used for many years, with its derivatives still found in embedded systems even after desktop computing shifted toward RISC and x86 architectures.

Motorola used even numbers for major revisions to the CPU core such as 68000, 68020, 68040 and 68060. The 68010 was a revised version of the 68000 with minor modifications to the core, and likewise the 68030 was a revised 68020 with some more powerful features, none of them significant enough to classify as a major upgrade to the core. The 68050 was reportedly "a minor upgrade of the 68040" that lost a battle for resources within Motorola. They considered the 68050 as not meriting the necessary investment in production of the part.

Ultimately, Motorola stopped investing in the MC680x0 family when everyone thought that RISC was the future and that CISC CPUs would be soon non competitive. So it formed an alliance in 1991 with Apple and IBM to switch to PowerPCs.

Applications

The Motorola 68000’s combination of a robust 32‑bit programming model and efficient 16‑bit data processing made it a versatile CPU that was deployed in numerous systems:

- Personal Computers and Workstations: Early Macintosh models, the Amiga, the Atari ST, and various Unix workstations leveraged the 68000 for its powerful instruction set and efficient memory addressing. Macintosh hardware description

- The Sinclair QL used the nearly identical 68008 (which featured an 8‑bit external data bus and a 20-bit address bus for cost savings).

- Video Game Consoles: Systems such as the Sega Genesis (Mega Drive) and arcade platforms utilized the 68000 to deliver high performance in graphics and sound processing. Genesis technical overview Genesis hardware notes

- Embedded Systems: The processor’s cost‑effectiveness and robust design made it popular for industrial controllers, laser printers, and other embedded devices. Even decades later, derivatives of the 68000 architecture (such as ColdFire and DragonBall) continue to be used in specialized applications.

Architecture

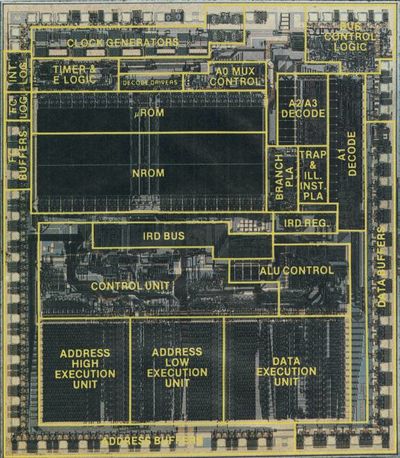

Microcode

Whereas the Z80 and the 6502 CPUs use a Decode ROM (PLA), the 68000 uses microcode instead.

To execute a machine instruction, the computer internally executes several simpler micro-instructions, specified by the microcode. In other words, microcode forms another layer between the machine instructions and the hardware.

The actual internal representation is a combination of "microcode" and "nanocode". The 68000 has 544 17-bit microcode words which dispaches to 366 68-bit nanocode words. Source

The microcode is a series of pointers into assorted microsubroutines in the nanocode. The nanocode performs the actual routing and selecting of registers and functions, and directs results. Decoding of an instruction's op code generates starting addresses in the microcode for the type of operation and the addressing mode. Source

See: Tech topic about a microcode-level 68000 core New 68k core in mame Motorola 68000 microcode

Hybrid 16/32‑Bit Design

The design implements a 32-bit instruction set, with 32-bit registers and a 16-bit data bus.

The address bus is 24 bits wide; while internal address computations occur using 32‑bit arithmetic, only the lower 24 bits are available on the physical pins. This design yields a flat memory model with a maximum addressable space of 16 MB without the complications of segmentation, simplifying both operating system design and application programming. But this gave trouble with later CPU models as it was a common trick for programs to store data in the 4th byte of an address (which simply would be ignored).

Internally, it uses a 16-bit data arithmetic logic unit (ALU) and two more 16-bit ALUs used mostly for addresses. At one time, one 32-bit address and one 16-bit data calculation can take place within the MC68000. This speeds instruction execution time considerably by processing addresses and data in parallel.

Register File

| Register | Size | Description | Notes |

|---|---|---|---|

| D0 - D7 | 32-bit | Data Registers | General-purpose registers for data manipulation (arithmetic, logic). Can be accessed as 8-bit (byte, `.B`), 16-bit (word, `.W`), or 32-bit (long word, `.L`). Not typically used directly for memory addressing. |

| A0 - A6 | 32-bit | Address Registers | General-purpose registers primarily used as pointers or index registers for memory addressing. Can be used for some 16-bit/32-bit arithmetic (operations usually affect the full 32 bits). Word operations typically sign-extend to 32 bits. |

| A7 (SP/USP/SSP) | 32-bit | Stack Pointer | Two physically separate registers exist: User Stack Pointer (USP) and Supervisor Stack Pointer (SSP). The processor uses the active one based on the S-bit (Supervisor state) in the Status Register.

Used implicitly by stack operations (`PEA`, `LINK`, `UNLK`, `MOVE to/from -(An)/(An)+`), subroutine calls (`JSR`, `BSR`), returns (`RTS`, `RTR`), and exceptions. |

| PC (Program Counter) | 32-bit | Points to the address of the next instruction to be fetched. | Although 32-bit internally, the original 68000 had a 24-bit address bus (16MB addressable space). Later variants (68010+) used more address lines. Modified by branches, jumps, calls, returns, exceptions. |

| SR (Status Register) | 16-bit | Holds processor status (Condition Codes) and system control bits. Divided into User Byte (CCR) and System Byte. User Byte (CCR - Condition Code Register, bits 0-7): * bit 0 - C (Carry) * bit 1 - V (Overflow) * bit 2 - Z (Zero) * bit 3 - N (Negative) * bit 4 - X (Extend) System Byte (bits 8-15): * bit 10,9,8 - I2, I1, I0 (Interrupt Mask) * bit 13 - S (Supervisor State) * bit 15 - T (Trace Mode) (Other bits reserved/unused in base 68000) |

User programs can typically only read/write the CCR (lower byte). System Byte modification requires Supervisor privileges.

X flag used for multi-precision arithmetic. S bit determines User/Supervisor mode (and active A7). T bit enables single-step tracing. I bits control interrupt priority level. |

Instruction Set

The Motorola 68000 was renowned for its rich, orthogonal instruction set:

- Operand Flexibility: Instructions can operate on bytes (.b), words (.w), and long words (.l) without restrictions imposed by the addressing mode. Even though arithmetic is executed in 16‑bit chunks, the compiler and assembly programmer can manipulate 32‑bit values seamlessly.

- Addressing Modes: The 68000 supports an extensive range of addressing modes—including register direct, register indirect (with post‑increment, pre‑decrement, offset, and index variations), immediate, absolute, and PC‑relative addressing—which enhances code density and simplifies the generation of position‑independent and reentrant code.

- Dyadic Operations: Most operations in the 68000’s CISC architecture are dyadic (i.e. they have a source and a destination), enabling complex operations in fewer instructions compared to earlier 8‑bit designs. In contrast, many arithmetic and logical operations on the Z80 CPU are designed around the accumulator register (A).

This comprehensive and flexible instruction set was one of the reasons the 68000 became popular in systems that required multitasking and graphical interfaces, such as early Macintosh and Amiga computers.

| Mnemonic | Size | Description | Operation | Condition Codes | ||||||

|---|---|---|---|---|---|---|---|---|---|---|

| B | W | L | X | N | Z | V | C | |||

| ABCD | B | Add Decimal with Extend | (Destination)⏨ + (Source)⏨ + X → Destination | * | U | * | U | * | ||

| ADD | B | W | L | Add Binary | (Destination) + (Source) → Destination | * | * | * | * | * |

| ADDA | W | L | Add Address | (Destination) + (Source) → Destination | – | – | – | – | – | |

| ADDI | B | W | L | Add Immediate | (Destination) + Immediate Data → Destination | * | * | * | * | * |

| ADDQ | B | W | L | Add Quick | (Destination) + Immediate Data → Destination | * | * | * | * | * |

| ADDX | B | W | L | Add Extended | (Destination) + (Source) + X → Destination | * | * | * | * | * |

| AND | B | W | L | AND Logical | (Destination) ∧ (Source) → Destination | – | * | * | 0 | 0 |

| ANDI | B | W | L | AND Immediate | (Destination) ∧ Immediate Data → Destination | – | * | * | 0 | 0 |

| ANDI to CCR | B | AND Immediate to Condition Codes | (Source) ∧ CCR → CCR | * | * | * | * | * | ||

| ANDI to SR | W | AND Immediate to Status Register | (Source) ∧ SR → SR | * | * | * | * | * | ||

| ASL, ASR | B | W | L | Arithmetic Shift | (Destination) Shifted by < count > → Destination | * | * | * | * | * |

| Bcc | Branch Conditionally | If cc then PC + d → PC | – | – | – | – | – | |||

| BCHG | B | L | Test a Bit and Change | ~(< bit number >) OF Destination → Z

~(< bit number >) OF Destination → < bit number > OF Destination |

– | – | * | – | – | |

| BCLR | B | L | Test a Bit and Clear | ~(< bit number >) OF Destination → Z

0 → < bit number > OF Destination |

– | – | * | – | – | |

| BRA | Branch Always | PC + d → PC | – | – | – | – | – | |||

| BSET | B | L | Test a Bit and Set | ~(< bit number >) OF Destination → Z

1 → < bit number > OF Destination |

– | – | * | – | – | |

| BSR | Branch to Subroutine | PC → (SP); PC + d → PC | – | – | – | – | – | |||

| BTST | B | L | Test a Bit | ~(< bit number >) OF Destination → Z | – | – | * | – | – | |

| CHK | W | Check Register Against Bounds | If Dn < 0 or Dn > (ea) then TRAP | – | * | U | U | U | ||

| CLR | B | W | L | Clear Operand | 0 → Destination | – | 0 | 1 | 0 | 0 |

| CMP | B | W | L | Compare | (Destination) - (Source) | – | * | * | * | * |

| CMPA | W | L | Compare Address | (Destination) - (Source) | – | * | * | * | * | |

| CMPI | B | W | L | Compare Immediate | (Destination) - Immediate Data | – | * | * | * | * |

| CMPM | B | W | L | Compare Memory | (Destination) - (Source) | – | * | * | * | * |

| DBcc | W | Test Condition, Decrement and Branch | If ~cc then Dn - 1 → Dn; if Dn ≠ -1 then PC + d → PC | – | – | – | – | – | ||

| DIVS | W | Signed Divide | (Destination) / (Source) → Destination | – | * | * | * | 0 | ||

| DIVU | W | Unsigned Divide | (Destination) / (Source) → Destination | – | * | * | * | 0 | ||

| EOR | B | W | L | Exclusive OR Logical | (Destination) ⊕ (Source) → Destination | – | * | * | 0 | 0 |

| EORI | B | W | L | Exclusive OR Immediate | (Destination) ⊕ Immediate Data → Destination | – | * | * | 0 | 0 |

| EORI to CCR | B | Exclusive OR Immediate to Condition Codes | (Source) ⊕ CCR → CCR | * | * | * | * | * | ||

| EORI to SR | W | Exclusive OR Immediate to Status Register | (Source) ⊕ SR → SR | * | * | * | * | * | ||

| EXG | L | Exchange Register | Rx ↔ Ry | – | – | – | – | – | ||

| EXT | W | L | Sign Extend | (Destination) Sign-Extended → Destination | – | * | * | 0 | 0 | |

| JMP | Jump | Destination → PC | – | – | – | – | – | |||

| JSR | Jump to Subroutine | PC → (SP); Destination → PC | – | – | – | – | – | |||

| LEA | L | Load Effective Address | < ea > → An | – | – | – | – | – | ||

| LINK | Link and Allocate | An → (SP); SP → An; SP + Displacement → SP | – | – | – | – | – | |||

| LSL, LSR | B | W | L | Logical Shift | (Destination) Shifted by < count > → Destination | * | * | * | 0 | * |

| MOVE | B | W | L | Move Data from Source to Destination | (Source) → Destination | – | * | * | 0 | 0 |

| MOVE to CCR | W | Move to Condition Code | (Source) → CCR | * | * | * | * | * | ||

| MOVE to SR | W | Move to Status Register | (Source) → SR | * | * | * | * | * | ||

| MOVE from SR | W | Move from the Status Register | SR → Destination | – | – | – | – | – | ||

| MOVE USP | L | Move User Stack Pointer | USP → An; An → USP | – | – | – | – | – | ||

| MOVEA | W | L | Move Address | (Source) → Destination | – | – | – | – | – | |

| MOVEM | W | L | Move Multiple Registers | Registers → Destination

(Source) → Registers |

– | – | – | – | – | |

| MOVEP | W | L | Move Peripheral Data | (Source) → Destination | – | – | – | – | – | |

| MOVEQ | L | Move Quick | Immediate Data → Destination | – | * | * | 0 | 0 | ||

| MULS | W | Signed Multiply | (Destination) × (Source) → Destination | – | * | * | 0 | 0 | ||

| MULU | W | Unsigned Multiply | (Destination) × (Source) → Destination | – | * | * | 0 | 0 | ||

| NBCD | B | Negate Decimal with Extend | -((Destination)⏨ - X) → Destination | * | U | * | U | * | ||

| NEG | B | W | L | Negate | 0 - (Destination) → Destination | * | * | * | * | * |

| NEGX | B | W | L | Negate with Extend | 0 - (Destination) - X → Destination | * | * | * | * | * |

| NOP | No Operation | – | – | – | – | – | – | |||

| NOT | B | W | L | Logical Complement | ~(Destination) → Destination | – | * | * | 0 | 0 |

| OR | B | W | L | Inclusive OR Logical | (Destination) ∨ (Source) → Destination | – | * | * | 0 | 0 |

| ORI | B | W | L | Inclusive OR Immediate | (Destination) ∨ Immediate Data → Destination | – | * | * | 0 | 0 |

| ORI to CCR | B | Inclusive OR Immediate to Condition Codes | (Source) ∨ CCR → CCR | * | * | * | * | * | ||

| ORI to SR | W | Inclusive OR Immediate to Status Register | (Source) ∨ SR → SR | * | * | * | * | * | ||

| PEA | L | Push Effective Address | < ea > → (SP) | – | – | – | – | – | ||

| RESET | Reset External Device | – | – | – | – | – | – | |||

| ROL, ROR | B | W | L | Rotate (Without Extend) | (Destination) Rotated by < count > → Destination | – | * | * | 0 | * |

| ROXL, ROXR | B | W | L | Rotate with Extend | (Destination) Rotated by < count > → Destination | * | * | * | 0 | * |

| RTE | Return from Exception | (SP) → SR; (SP) → PC | * | * | * | * | * | |||

| RTR | Return and Restore Condition Codes | (SP) → CC; (SP) → PC | * | * | * | * | * | |||

| RTS | Return from Subroutine | (SP) → PC | – | – | – | – | – | |||

| SBCD | B | Subtract Decimal with Extend | (Destination)⏨ - (Source)⏨ - X → Destination | * | U | * | U | * | ||

| Scc | B | Set According to Condition | If cc then 1’s → Destination else 0’s → Destination | – | – | – | – | – | ||

| STOP | W | Load Status Register and Stop | Immediate Data → SR; STOP | * | * | * | * | * | ||

| SUB | B | W | L | Subtract Binary | (Destination) - (Source) → Destination | * | * | * | * | * |

| SUBA | W | L | Subtract Address | (Destination) - (Source) → Destination | – | – | – | – | – | |

| SUBI | B | W | L | Subtract Immediate | (Destination) - Immediate Data → Destination | * | * | * | * | * |

| SUBQ | B | W | L | Subtract Quick | (Destination) - Immediate Data → Destination | * | * | * | * | * |

| SUBX | B | W | L | Subtract with Extend | (Destination) - (Source) - X → Destination | * | * | * | * | * |

| SWAP | W | Swap Register Halves | Register [31:16] ↔ Register [15:0] | – | * | * | 0 | 0 | ||

| TAS | B | Test and Set an Operand | (Destination) Tested → CC; 1 → [7] OF Destination | – | * | * | 0 | 0 | ||

| TRAP | Trap | PC → (SSP); SR → (SSP); (Vector) → PC | – | – | – | – | – | |||

| TRAPV | Trap on Overflow | If V then TRAP | – | – | – | – | – | |||

| TST | B | W | L | Test an Operand | (Destination) Tested → CC | – | * | * | 0 | 0 |

| UNLK | Unlink | An → SP; (SP) → An | – | – | – | – | – | |||

Legend:

- ∧: logical AND

- ∨: logical OR

- ⊕: logical exclusive OR

- ~: logical complement

Condition codes:

- *: affected

- –: unaffected

- 0: cleared

- 1: set

- U: undefined

Bcc, DBcc and Scc families of instructions make use of the CCR. The following table lists all the possible conditions we can test:

| Instruction | Full name | Tested condition | Notes |

|---|---|---|---|

| CC | Carry Clear | C == 0 | |

| CS | Carry Set | C == 1 | |

| EQ | EQual | Z == 1 | |

| F | False | Always false | Not available for Bcc |

| GE | Greater or Equal | N == V | |

| GT | Greater Than | N == V and Z == 0 | |

| HI | HIgher than | C == 0 and Z == 0 | |

| LE | Less or Equal | Z == 1 or N != V | |

| LS | Lower or Same | C == 1 or Z == 1 | |

| LT | Less Than | N != V | |

| MI | MInus | N == 1 | |

| NE | Not Equal | Z == 0 | |

| PL | PLus | N == 0 | |

| T | True | Always true | Not available for Bcc |

| VC | oVerflow Clear | V == 0 | |

| VS | oVerflow Set | V == 1 |

Block Diagram

CPU Pinout

The 68000 doesn't need an A0 pin, because it uses 2 DS (LDS & UDS) signals - each being responsible for its byte on 16-bit data bus. Source

Floating Point Unit

Unlike the Intel 8086, the Motorola 68000 lacked native support for an FPU co-processor.

Motorola introduced the 68881 FPU in 1984, which could function as a peripheral alongside the 68000. But it was primarily designed to integrate seamlessly with the 32-bit 68020, taking advantage of its co-processor interface.

Links

- Motorola MC68000 CPU User's Manual

- MC68000 Advance Information

- 68000 - Programmer's Instant Reference Card

- MarkeyJester’s Motorola 68000 Beginner’s Tutorial

- Learn Assembly Programming with ChibiAkumas Multi-platform 68000 tutorial

- Decoding m68k opcodes

- Motorola 68000 oral history panel

- Part 1 Part 2 Part 3 Design philosophy behind Motorola's MC68000

- Full list of 68k patents

- 68k instructions timings

- Yet Another Cycle Hunting Table

- Instruction Prefetch documentation

- Tom Harte's SingleStepTests