Difference between revisions of "Emulator evaluation tools"

(→Diagnostics) |

|||

| (3 intermediate revisions by the same user not shown) | |||

| Line 11: | Line 11: | ||

*[[FDC|765 FDC]] is bloated with 40 pins, compared to 28 pins for the WD1772 FDC used in the [[Atari ST]]. It is also a black box internally, while the [[C64]] uses a regular 6502 (with its own ROM and RAM) as FDC. | *[[FDC|765 FDC]] is bloated with 40 pins, compared to 28 pins for the WD1772 FDC used in the [[Atari ST]]. It is also a black box internally, while the [[C64]] uses a regular 6502 (with its own ROM and RAM) as FDC. | ||

| − | And unlike the [[ZX Spectrum]] and the [[MSX]], on the Amstrad CPC and Plus things | + | And unlike the [[ZX Spectrum]] and the [[MSX]], on the Amstrad CPC and Plus things often go catastrophically wrong if timings are not accurately emulated. |

Thankfully, many tools and tests exist to help emulation authors. | Thankfully, many tools and tests exist to help emulation authors. | ||

| Line 34: | Line 34: | ||

== Diagnostics == | == Diagnostics == | ||

| − | *[https://www.cpc-power.com/index.php?page=detail&num=5113 Amstest] [https://www.cpc-power.com/index.php?page=detail&num=17932 Amstrad Diagnostics] [https://www.cpcwiki.eu/forum/amstrad-cpc-hardware/amstrad-diagnostics-rom/msg243665/] [https://www.cpcwiki.eu/forum/software-related/8255-manufacturer-detection/] [https://www.cpc-power.com/index.php?page=detail&num=6545 STS SysInfo] [https://www.cpc-power.com/index.php?page=database&r1=1&lemot=test%20crtc%20v Test CRTC type] [http://quasar.cpcscene.net/doku.php?id=coding:test_crtc] [http://cpc.sylvestre.org/technique/technique_identifier_crtc.html Identifying CRTC visually] [https://www.cpc-power.com/index.php?page=detail&num=11446 Basic Program Status Window] [https://www.cpc-power.com/index.php?page=detail&num=12584 Version du Firmware Basic] | + | *[https://auamstrad.es/software/aua-utilidades/ AUA Utilidades] [https://www.cpc-power.com/index.php?page=detail&num=5113 Amstest] [https://www.cpc-power.com/index.php?page=detail&num=17932 Amstrad Diagnostics] [https://www.cpcwiki.eu/forum/amstrad-cpc-hardware/amstrad-diagnostics-rom/msg243665/] [https://www.cpcwiki.eu/forum/software-related/8255-manufacturer-detection/] [https://www.cpc-power.com/index.php?page=detail&num=6545 STS SysInfo] [https://www.cpc-power.com/index.php?page=database&r1=1&lemot=test%20crtc%20v Test CRTC type] [http://quasar.cpcscene.net/doku.php?id=coding:test_crtc] [http://cpc.sylvestre.org/technique/technique_identifier_crtc.html Identifying CRTC visually] [https://www.cpc-power.com/index.php?page=detail&num=11446 Basic Program Status Window] [https://www.cpc-power.com/index.php?page=detail&num=12584 Version du Firmware Basic] |

*[http://www.symbos.de/appinfo.htm?00061 SyMon] [http://www.symbos.de/appinfo.htm?00047 HexE] [https://www.cpc-power.com/index.php?page=detail&num=6987 RAM Expansion Test] [https://www.cpc-power.com/index.php?page=detail&num=14833 MemTest] [https://www.cpc-power.com/index.php?page=detail&num=14834 RAM Test CRTC4] [https://www.cpcwiki.eu/forum/technical-support/test-ram-de-mcleod-ideafix/ Test RAM de McLeod Ideafix] [https://www.cpc-power.com/index.php?page=detail&num=15739 RAM Check] [https://www.cpc-power.com/index.php?page=detail&num=13386 Testprogram For All ERAM] [https://www.cpc-power.com/index.php?page=detail&num=16010 Test RAM Basic] [https://www.cpc-power.com/index.php?page=detail&num=19185 Xenon 2] [https://www.cpc-power.com/index.php?page=detail&num=12188 Take On Me] [https://www.cpc-power.com/index.php?page=detail&num=14339 Trololo Experiments] [https://www.cpc-power.com/index.php?page=detail&num=19406 Still The One] [https://www.cpc-power.com/index.php?page=detail&num=16084 Post Scriptum] [https://www.cpc-power.com/index.php?page=detail&num=18658 Onescreen Colonies #2 256K] [https://www.cpc-power.com/index.php?page=detail&num=15985 A tribute to the sisters] [https://amstrad-ggp.itch.io/mightysf Mighty Steel Fighters] [https://cpcrulez.fr/info-chany-enhanced_edition.htm Chany 512K cracks] [https://www.cpc-power.com/index.php?page=detail&num=14814 Anti-Multiface] [https://www.cpc-power.com/cpcarchives/index.php?page=articles&num=151 Expanded RAM software list] RAM exercisers | *[http://www.symbos.de/appinfo.htm?00061 SyMon] [http://www.symbos.de/appinfo.htm?00047 HexE] [https://www.cpc-power.com/index.php?page=detail&num=6987 RAM Expansion Test] [https://www.cpc-power.com/index.php?page=detail&num=14833 MemTest] [https://www.cpc-power.com/index.php?page=detail&num=14834 RAM Test CRTC4] [https://www.cpcwiki.eu/forum/technical-support/test-ram-de-mcleod-ideafix/ Test RAM de McLeod Ideafix] [https://www.cpc-power.com/index.php?page=detail&num=15739 RAM Check] [https://www.cpc-power.com/index.php?page=detail&num=13386 Testprogram For All ERAM] [https://www.cpc-power.com/index.php?page=detail&num=16010 Test RAM Basic] [https://www.cpc-power.com/index.php?page=detail&num=19185 Xenon 2] [https://www.cpc-power.com/index.php?page=detail&num=12188 Take On Me] [https://www.cpc-power.com/index.php?page=detail&num=14339 Trololo Experiments] [https://www.cpc-power.com/index.php?page=detail&num=19406 Still The One] [https://www.cpc-power.com/index.php?page=detail&num=16084 Post Scriptum] [https://www.cpc-power.com/index.php?page=detail&num=18658 Onescreen Colonies #2 256K] [https://www.cpc-power.com/index.php?page=detail&num=15985 A tribute to the sisters] [https://amstrad-ggp.itch.io/mightysf Mighty Steel Fighters] [https://cpcrulez.fr/info-chany-enhanced_edition.htm Chany 512K cracks] [https://www.cpc-power.com/index.php?page=detail&num=14814 Anti-Multiface] [https://www.cpc-power.com/cpcarchives/index.php?page=articles&num=151 Expanded RAM software list] RAM exercisers | ||

*[https://www.cpc-power.com/index.php?page=detail&num=15975 FutureOS] [https://www.cpc-power.com/index.php?page=detail&num=4174 CP/M Plus] [https://www.cpcwiki.eu/forum/software-related/what-software-requires-c3-ram-banking/msg246339/#msg246339 Fuzix OS] [https://www.cpc-power.com/index.php?page=detail&num=10030 Phortem] [https://www.cpcwiki.eu/forum/software-related/what-software-requires-c3-ram-banking/msg246582/#msg246582 PhX] [https://www.cpc-power.com/index.php?page=detail&num=19308 DSC4] [https://www.cpc-power.com/index.php?page=detail&num=7270 Pac-Man Emulator] Problematic [[PAL16L8|RAM mode &C3]] on CPC464/664 | *[https://www.cpc-power.com/index.php?page=detail&num=15975 FutureOS] [https://www.cpc-power.com/index.php?page=detail&num=4174 CP/M Plus] [https://www.cpcwiki.eu/forum/software-related/what-software-requires-c3-ram-banking/msg246339/#msg246339 Fuzix OS] [https://www.cpc-power.com/index.php?page=detail&num=10030 Phortem] [https://www.cpcwiki.eu/forum/software-related/what-software-requires-c3-ram-banking/msg246582/#msg246582 PhX] [https://www.cpc-power.com/index.php?page=detail&num=19308 DSC4] [https://www.cpc-power.com/index.php?page=detail&num=7270 Pac-Man Emulator] Problematic [[PAL16L8|RAM mode &C3]] on CPC464/664 | ||

| Line 155: | Line 155: | ||

The way to cause the RAM refresh to fail in both a Plus or normal CPC is simply to stop a few bits of the CRTC address changing (ie. never refresh the selected area). | The way to cause the RAM refresh to fail in both a Plus or normal CPC is simply to stop a few bits of the CRTC address changing (ie. never refresh the selected area). | ||

Generally, only the Row address needs to be cycled, so stopping MA0 through MA7 from changing, and stopping the CPU from reading those rows, will cause data to be lost, quite quickly (generally around 4ms). | Generally, only the Row address needs to be cycled, so stopping MA0 through MA7 from changing, and stopping the CPU from reading those rows, will cause data to be lost, quite quickly (generally around 4ms). | ||

| + | *Detecting corruption in the PSG registers when a register write is not validated. [https://www.cpcwiki.eu/forum/programming/interesting-walkthrough-video-coding-a-pet-to-play-samples-at-60khz/msg250874/#msg250874 Source] | ||

*Playing with the "floating" bus. Using Z80 read I/O commands to write to chip registers. Accessing ghost registers. Using undocumented I/O ports. Writing to multiple chips simultaneously. Changing PPI and PSG ports direction. | *Playing with the "floating" bus. Using Z80 read I/O commands to write to chip registers. Accessing ghost registers. Using undocumented I/O ports. Writing to multiple chips simultaneously. Changing PPI and PSG ports direction. | ||

*Focusing on the minute details in [[Z80]], [[CRTC]], [[8255|PPI]] and [[PAL16L8|PAL]] chips. They are most often wrong in emulators. | *Focusing on the minute details in [[Z80]], [[CRTC]], [[8255|PPI]] and [[PAL16L8|PAL]] chips. They are most often wrong in emulators. | ||

Latest revision as of 08:14, 20 May 2025

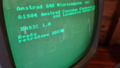

While it is easy to create an approximate emulation, the Amstrad CPC and Plus are very difficult to emulate accurately.

Each chip has its own challenges:

- Z80 is a bloated architecture, with lots of special cases and complex bus logic. The difference with the lean GBZ80 and 6502 is striking.

- CRTC has a character-based addressing logic, many incompatible chip implementations, and requires accurate VDU emulation too.

- Gate Array has a weird interrupt system and adds an unnecessary layer of complexity to sync signals.

- ASIC is buggy and lacks precise documentation.

- Memory management is overly complex and limited.

- PPI has more functionalities than what the CPC needs.

- PSG cannot be accessed directly as it is behind the PPI. It is simple to emulate though, but it cannot do much.

- 765 FDC is bloated with 40 pins, compared to 28 pins for the WD1772 FDC used in the Atari ST. It is also a black box internally, while the C64 uses a regular 6502 (with its own ROM and RAM) as FDC.

And unlike the ZX Spectrum and the MSX, on the Amstrad CPC and Plus things often go catastrophically wrong if timings are not accurately emulated.

Thankfully, many tools and tests exist to help emulation authors.

Contents

Quick evaluation

- From Scratch demo with reference images (CRTC 1): Media:From Scratch logo.png Media:From Scratch tetris.png Media:From Scratch ovl.png

- DSC4 v2 demo with reference images (CRTC 1): Media:DSC4 reference1.png Media:DSC4 reference2.png Technical explanation

- Other World 3 demo with reference image (CRTC 0/1): Media:Other World 3.png

- BSC7 Interlace demo with reference image (CRTC 0/2/3/4): Media:BSC7 reference.png

Categories

Z80 CPU

- 🔥Raxoft tests (CPC port of z80test) Redcode Z80 tests list with expected results Z80 XCF Flavor z80type ZEX Z80 CPU instruction set exercisers

- Arkanoid Boulder Dash The Great Escape Using Z80 Interrupt Mode 2

- Trailblazer (using HALT) L'anneau de Zengara (using Z80 register R) Light Corridor (Z80 useless instruction prefixes) Dogsbody (accessing non-standard I/O ports) Pinball Dreams (Z80 NMOS only)

- Weird Z80 behaviour I/O port allocation I/O access Technical documentation

Diagnostics

- AUA Utilidades Amstest Amstrad Diagnostics [1] [2] STS SysInfo Test CRTC type [3] Identifying CRTC visually Basic Program Status Window Version du Firmware Basic

- SyMon HexE RAM Expansion Test MemTest RAM Test CRTC4 Test RAM de McLeod Ideafix RAM Check Testprogram For All ERAM Test RAM Basic Xenon 2 Take On Me Trololo Experiments Still The One Post Scriptum Onescreen Colonies #2 256K A tribute to the sisters Mighty Steel Fighters Chany 512K cracks Anti-Multiface Expanded RAM software list RAM exercisers

- FutureOS CP/M Plus Fuzix OS Phortem PhX DSC4 Pac-Man Emulator Problematic RAM mode &C3 on CPC464/664

- 🔥Kevin Thacker's "Acid tests" suite Older version Forum thread Tests results in ACE Collection of tests which are used to verify emulators operation against real CPC, Plus and expansions

- 🔥Richard Wilson's Plus Test suite [4] CPC and CPC+ Emulator test suite (including Instruction and Interrupt timing tests)

Amstrad Plus

- Arnold 5 Diagnostic Cartridge Software Demonstrator 4096 Colors Preview 4096K tester File:Roudoudou CPR tests.zip [5] No Exit (uninitialised stack pointer) Pang (RMR2) 3DManiaks 2 (512K) Tennis Cup 2 (analogue joystick) Plus testing tools

- Delirium Tremens Delirium Tremens running on real hardware Bulles Funerapolis X-mas 2008 USS Cygnus 192 To test hardware sprites

- 6128 Plus DMA Fairy Soundtracker DMA To test DMA sound

- CRTC3 To test RAM expansion compatibility with ASIC Source

- Arnoldemu T&J Sylvestre Longshot [6] Offset [7] Plus Vectored Interrupt Bug Plus hardware bugs documented

- L'Aigle d'Or le Retour Bumpy's Arcade Fantasy Kick Boxing Gold D.Day Striker in the Crypts of Trogan Prehistorik II CPC Demos with Plus features To test Amstrad Plus enhancement of CPC software

- Plus Games Demos for Plus only Search filters to verify the entire Plus software library

Colorimetry

- CPC DiAG Raster Toutes les couleurs du CPC Couleurs Les split-rasters Mir'Color Test Interlace Color Infinite Colours Mode 1 Tramage et Choix des Couleurs FED Colour calibration

- Minor difference in colorimetry between CPC and Plus On CPC (not Plus!), green half-intensity is significantly higher than red and blue half-intensities

- Major difference in colorimetry between the real Amstrad displays and emulators display. CPC DiAG shows clearly why, by demonstrating the weak response of Amstrad monitors to the Red component:

- CPC DiAG also shows that the primary colours themselves are a bit different. Blue is more vivid and Green is less fluorescent on Amstrad displays.

- Colours are less saturated and black is not as profound on CRT monitors than they are on modern displays.

- On CRT displays, bright pixels will spill on their neighbours while dark pixels will get eaten by their neighbours (ie. bright pixels are bigger than dark pixels on CRT displays), affecting dithered colours. This effect is absent on LCD displays.

- The usual scanline effect of CRT monitors is barely noticeable on the Amstrad CTM colour monitor. But it is very pronounced on Amstrad monochrome monitors.

- The slot mask is the texture that is visible in the CTM colour monitor. CRT masks do not exist on monochrome monitors.

- To test emulators VSYNC (screen-tearing and skipped frames): Source

border 22,17:ink 0,4,9:speed ink 1,1

Graphics

- 🔥Shakerland Ultra accurate CRTC documentation and its associated CPC testing tool

- 5KB 2 (tweakable demo) HSYNC test CRTC Programmierung Côté Gamers Screen Effect Blitter File:CheshireCat - Scroll hard en Basic.dsk [8] Out-Screen II CRTC editor Control del CRT CRTC testing tools

- Vertical and Horizontal 1-pixel mode1 hardware scroll for all CRTCs File:Lister-of-smeg vertscroll4.dsk Smooth CRTC Register 3 scrolling test Skate Wars Jinks Out of this World Killer Cobra Edge Grinder Relentless Corsair Trainer Warhawk Mission Genocide Axys Red Sunset Ghosts'n Goblins Danger Street Profanation Legend of Kage Super Cauldron Smooth CRTC R3/R5 hardware scrolling

- BSC 91 Voyage 1993 OVL '96 Byte 98 Divine Paradise Power System Prodatron Longshot Amazing KKB First Hage's First New Age Flore Dentro Chany Dream End S&Koh Overflow Previews Mystery Little One Freedelire Spy Hunter Scroller Big'O Full'O Dem'O Sea You Soon Plasma Wobbler Mad Rast Odyssey Synergy Early CRTC demos

- Ze Meeting 2003 Camembert 4 DemoIzArt Not Dead Croco Chanel Tire Au Flan Arôme Tomate Twistimus DTC Synergy 2 CRTC demos from 2000s

- OSC #0 OSC #1 Still Rising Still the Bests Still Scrolling River Scroll Scroll Factory Battro Bloc Us Wake Up Wunderbar Cookie Yet Another Plasma Isometrikum Logon's Run Octopus Pocus Sugarlumps CRTC demos from 2010s

- OSC #2 OSC #3 Stand Up The One Swingin' Return of the Droid Mike's Scrollers Foursome Checkmate Debris Ghost Nop Latest CRTC demos

- Points Barres (Mode 3) New Mode "Mode 5" Viewer Raster Slideshow Brutal Deluxe Rhino-Raster Split-Rasters Test CRTC1 Crazy Ball Trailblazer Fugitif Sudoku Master Flush Wishes You a Happy New Year Pixel Free Overscan Megatext Gozeur Intro 2 Interlace viewer Interlaced 800x600 Interlace Climax Kvety Flipraster Perfect Pix Paint Bat-Moule Tetris Imperial Mahjong Special graphics modes Mode EGX Mode R Mode 5 Technical explanations

- Mire Chany Dream 5 4 Sins TV Noise Climax-G Nice Picture Show Fatal Beauties JavaCPC Overscan Pixel Nation Twinblast MCS 6 Schadel Scandinavian Flag Kill JLCS Deleting Disc Plasma Pas Cher Wavy Vagues sur l'écran Bildschirmverzerrer Thunder Blade (292 lines) Bonanza Bros (295 lines) Turrican (296 lines) Wonder Boy (296 lines) Sliders (330 lines) Rastan (336 lines) Bomb Jack remake (over-overscan) To test the VDU

- Street Fighter II proto (crtc0) Octoplex (crtc1) Dynamic Duo (crtc1) Druid II (crtc1) Legend of Steel (crtc1) The Living Daylights (crtc1) FMR (crtc1) Some known bugs on real CRTCs

- Welcom-X 2 (crtc0) Madness (crtc1) 5KB 1 (crtc1) Scrolling Hard Vertical (crtc2) Some programs that only run correctly on one type of CRTC

Audio

- Trantor 3D Starfighter Treasure Island Dizzy Ghost Hunters Super Robin Hood Advanced Pinball Simulator Jet Bike Simulator Grand Prix Simulator Darts 180 Killapede Startest Jail Break Robocop Chase HQ Shinobi Fly Spy Meltdown Throne Legacy Léon Marchand's Olympic Challenge Just Get 9 4-Bit Digi Try OctoBear Speech Software English vocal sounds

- El Enigma de Aceps Le Manoir de Mortvielle Etrange Castel Forteresse Canadair L'île Jaws Holocauste Apocalypse Punk Star Afteroids Amstroids Hold-Up Fire & Forget Xyphoes Fantasy Spectra Space Race Yao demo Terrific Face Hugger Ultimate Smallest Scroll Xenon Musik100 Digital Synthesizer Echosoft Mega Sound Digitracker NGS Other software sound effects Audio-tape included software list

- RUN! Now that's what I call Chip Tunes Amstream Automated Music Player We Are All Old Anthology AYC Sound Shap Audio Amstrad CPC Mix YM!Rulez (real hardware recordings) Soundtrakker 128k ST128 Song Modules by BSC Starkos Starkos Song Modules Ams'Orgue Sintetizador de Sonidos To test the PSG emulation

Peripherals

- TMPI software list Multilingual SSA-1 software list Dk'Tronics software list English-only speech synthesizers

- Cocoon Player Bordelik 4 Digital Orgasm Bloood Megamix 2020 Drumming CPC Digitracker Symbiosis Prodatron MDL packs File:DigiTracker Amdrum.zip [9] Amdrum To test Digiblaster and Amdrum soundcards emulation

- VGMplay OPL3 VGM pack SID Player MidiTrack Performer To test Willy OPL3, RSF3 SID and EMR MIDI Interface (RSF3) soundcards emulation

- West Phaser Gunstick Trojan LP-1 To test lightguns and lightpens connected to joystick port Magnum Light Phaser SkeetShoot The Enforcer Dk'Tronics Light Pen Light Pen Mark II Dart Light Pen FutureOS To test lightguns and lightpens connected to expansion port

- The Key Le Manoir de Mortvielle Pro-Design Cherry Paint EasiArt GPaint AMX Art Advanced OCP Art Studio Max Desktop Worktop DES Stream2 FutureOS SymbOS To test AMX Mouse and Albireo USB mouse emulation

- Tasword Tasprint Print Master ProText ProType ProPrint Miraprint Qualitas Plus BrunWord CPC-Word MicroDesign Page Printer Stop Press (AMX Pagemaker) X-Press Page Publisher PowerPage 128 Page Setter 64 StarMouse Impr'Image Speedtrans screen dump Kdump Printer Pac II Impression RSX Imprimante Scrypte Machine à écrire DemoImp PrintIt Wordpad To test printer emulation

- HDCPM FutureOS SymbOS UniDOS UniLoad To test RTC and mass-storage emulation

- RulezCharge CPChessNet Ewen KCNet utilities NsLookUp SymTel WGet SymbOS UniDOS To test the network emulation

- X-MEM FW 32 Roms Booster Roman CatRun CowSay iMPdraw iMPtiles Graph'OS Nirvana Utopia Hexam Orgams YANCC HDCPM FutureOS SymbOS UniDOS ROM Games To test ROMboard emulation

- Alcon 2020 Hyperdrive Puzzle Bobble Revenge of Trasmoz Crazy Piri Chronicle Converted GX4000 Software FutureOS SymbOS UniDOS Cartridge Creator To test Plus2CPC or compatible (Play2CPC, Cartridge Emulator, M4 Board) CPC cartridge slot expansion

- Multiface Protector Anti-Multiface II software list RX 220 War in Middle Earth Zap't'Balls advanced The Insider MF2RR Technical documentation [10] To test Multiface II emulation

- LensLok Dandanator 8bit Printer Ports Exotic hardware components that are essential for some CPC software and should therefore be emulated

- Everything else is a nice bonus

Note: Open standards like Albireo (CH376 USB and mass storage) and Net4CPC (W5100S Ethernet) should be favored over proprietary protocols (Multiplay, Symbiface 3, M4 Board)

Copy-protection

- FDC test suite Disk drive tests CDT/TZX test suite Set of tests by arnoldemu Various dump formats (CDT, TZX, CSW, VOC, WAV, MP3, DSK, HFE, IPF, SCP, etc...) IPF dumps CT-RAW dumps SCP dumps

- Azimut Locator Tape Speed Checker Motor Control Odd Border Ultra Son Catalogueur de Cassettes Tape Utility Soft-Lok Soft-Arc Deconnect NoAMSDOS software list Computer Hits Marmelade Mickey Mouse Basil Mask Split Personalities Frank Bruno's Boxing Baudload software list Keytone software list Tape Counter software list Brundij Loading Screens slideshows Tape Deck To test Tape emulation

- Musical Loader FatMag 2 FatMag 2 technical analysis 5KB 3 Backtro Unique The Demo Fres Fighter II Turbo CPC 30th Anniversary Midline Process Can Robots Take Control PhX Batman Forever Pinball Dreams R-Type 128K Nheredia Doomsday Lost Echoes The Elves of Maroland Orion Prime Musical loader, Multi-drives, 3.5 inch (dual-head and 80 tracks) floppy drives support House of Usher (5.25 inch) ParaDOS software list Triple-format CPC/+3/PCW

- RPM DskTest Discover Dir Doktor Optimize Crazy Dlfrsilver Dump Tool Test Suite Format II Magic Transfert Magic DOS DOS-copy ParaDOS Xexor Discology Hercule II OddJob DiscKit Master Disc UltraDisc Disc+Ultra Disc'o'Magic Crime Multi Mark Demonstration of KBI protection Protector To test FDC emulation

- FatMag (HFE version) BND4 Invitro (sick mode) Open Tower Defense Rigorous FDC tests by Roudoudou Disk Swapping Autodetect software list Superpix Bad Mag Issue 2 Disk swapping detection Unique Diskmaker (generating discs in noiseload format) Big Cheese 2 (FDC VU-meter effect) Sphaira (accessing the 3rd drive) The Shadows of Sergoth (unformatted track)

- Weak Sectors Custom Gaps Custom Gap2 Sector SizeX Sector Size8 Sector Size7 Sector Size6 Sector Erased 64 Sectors Overlap Custom Rémi Herbulot Brice Rivé Rubi MBC Protected software lists

- Prehistorik Profession Détective Emlyn Hugues Arcade Quiz Other copy-protection schemes Dark Sceptre Krypton Factor Works only on older floppy drives TokiMap Technical explanation Unreliable FDC loader

- 1001 BC Scott Winder Reporter Holocauste Speedlock AAAA Destructive copy-protection Sir Lancelot Secret Defense M'enfin Turbo Cup Erebus Le Passager du Temps Anti-copy bug software list Exotic copy-protection MotorON software list

- Protection schemes documented Gaps Latis LensLok Copy-protection in EDSK images Implementation in SugarBox emulator FDC blog articles Autoboot Amsdos disk format Disk structure DiscSys Speedlock K7 1987 Speedlock D7 1989 Technical explanations

Other

- Into the Eagle's Nest Technical explanation Floating bus making the bottom border appear black on CPC, purple on 464+ and green on 6128+

- The Abduction of Oscar Z Technical explanation Neat unintended colour gradient effect on non-CTM monitors

- The Eternal Light Druid & Droid Paulina's Potions Harrier Attack Reloaded Claudia BMP Converter Snoozing Programs that only run fine on flawed emulators but are broken on real machines

- Equalizor Revolog Technical explanation Some believe it could be a random hardware bug of CRTC1 chip. But it could also be explained by the LD A,R instruction which is known to be buggy on NMOS Z80 when interrupted.

- Prehistorik II Uwol Screen calibration Get Dexter Different screen transition effect depending on the detected CRTC type Borderline Different demo depending on the detected CRTC type

- Space Racer Bob Winner Sapiens (Tape) Mata Hari (Tape) Thai Boxing CPC keyboard detection Jungle Jane 3D Megacode Firmware detection

- The Untouchables Batman The Movie Turrican Technical explanation CPC keyboard clash Thunder Blade (6 keys) Agent X II (7 keys) Wishing-Well (8 keys) Score 3020 (9 keys) Simultaneous keypresses for cheat mode

- Raytracing in BASIC Reliefs Mathématiques Cherry Blossom Deuligne Julia Fractal Rosetta Mandelbrot Rosetta Pi Spigot Life Highway To Hell Chain Overflow Tome 2 Montre Tape Counter software list To benchmark emulators using their fullspeed mode

Emulator detection methods

If you are a programmer who wants to promote usage of real CPC computers, you can detect CPC emulators by:

- Checking if the memory is initialised with zeroes, as RAM in real machines is not initialised during boot. Source

- Configuring the CRTC to stop refreshing part of the RAM. This behaviour has never been emulated. Source

The way to cause the RAM refresh to fail in both a Plus or normal CPC is simply to stop a few bits of the CRTC address changing (ie. never refresh the selected area). Generally, only the Row address needs to be cycled, so stopping MA0 through MA7 from changing, and stopping the CPU from reading those rows, will cause data to be lost, quite quickly (generally around 4ms).

- Detecting corruption in the PSG registers when a register write is not validated. Source

- Playing with the "floating" bus. Using Z80 read I/O commands to write to chip registers. Accessing ghost registers. Using undocumented I/O ports. Writing to multiple chips simultaneously. Changing PPI and PSG ports direction.

- Focusing on the minute details in Z80, CRTC, PPI and PAL chips. They are most often wrong in emulators.

- Examining the FDC chip. It is only replicated more or less superficially in all emulators because the internals of the chip are still unknown. Many emulators don't even support the FDC SCAN or FORMAT TRACK commands.

Combining these methods will definitely get you a 100% success rate in detecting emulators, even the toughest ones.

Additionally, an Emulator IDs system is available for easier detection of CPC emulators.

On ZX Spectrum, gamedevs are challenging emulators real hard with titles like MEMPTR Snake, Super HALT Invaders Test and Chromatrons Attack.